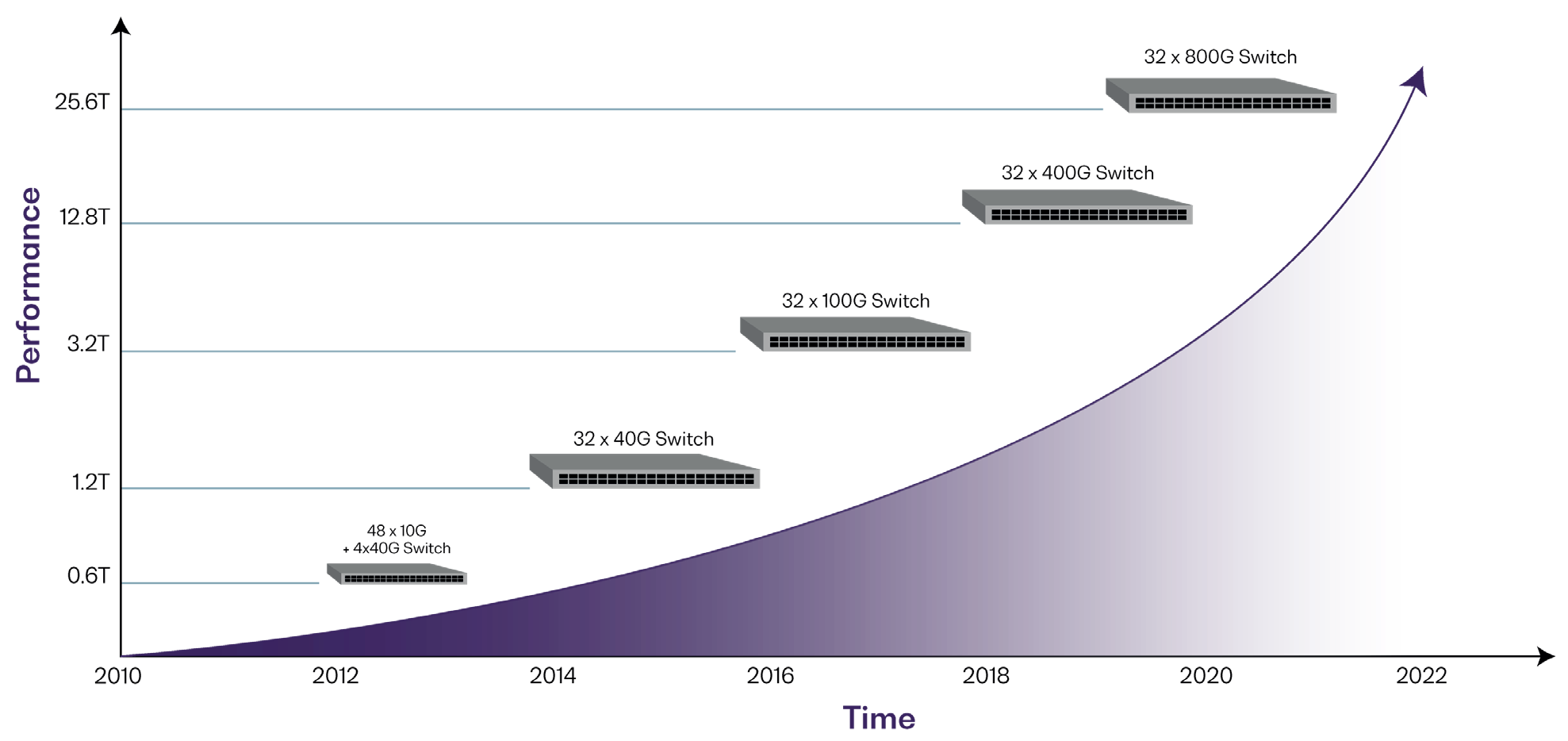

随着数据中心、机器学习和人工智能(AI)应用的快速发展,网络设备需要快速传输大量数据。因此,网络交换机的带宽需求在过去十年中增长了超过8000%。如图1所示,交换机的速度需求从2010年的320Gb/s增长到2022年的25.6Tb/s,并且很快将需要超过51.2Tb/s的带宽。

图1为了支持数据密集型应用,光设备的需求快速增长,推动了对更高性能、更高带宽网络交换机的需求。

如果继续使用当前的可插拔模块方法(即将模块插入机架式交换机的前面板),实现超过25.6Tb/s的高通道数将极具挑战性。在这些高带宽下使用可插拔模块会导致在将电信号从前面板后方传输到交换机ASIC(应用特定集成电路)时出现较大的能量损失,并且需要高功耗的信号处理来克服通道损伤。这些问题直接导致了高功耗以及与冷却可插拔光收发器和交换机相关的高运营成本。

为了应对这些挑战,消除数据传输瓶颈,光工程师正在开发更高效的方法,将光通道更接近电子设备。许多大型科技公司和光标准组织支持将收发器从前面板移除,创建一个将数据直接传输到电气交换结构的单一封装设备。这种技术被称为共封装光学(CPO)设备,可以在不显著增加功耗或收发器占地面积的情况下增加带宽,因为光学和电子元件直接相邻,位于同一个封装组件中。这种设计最小化了传输损耗,降低了信号处理需求,提供了最低的每比特数据传输功耗。

与任何新技术一样,工程师不仅需要解决开发这些实际设备的复杂性,还需要具备能够快速测试这些高通道密度设备功能的仪器。

本文档概述了正在进行的工作,以确保共封装光学设备在各种高带宽应用中的互操作性,并讨论了如何应对这一新技术带来的测试挑战。

确保共封装光学(CPO)设备的互操作性与标准化

目前,光互连论坛(Optical Internetworking Forum,简称OIF)和板载光学联盟(Consortium for On-Board Optics,简称COBO)正在迭代共封装光学设备开发的框架和规范文档。从高层次来看,OIF框架专注于解决光学和电气通信接口共封装的应用领域和技术考量。该框架还提供了许多技术考量,用于设计能够满足在带宽需求增加时降低功耗目标的共封装光学设备。

OIF还有一个相关的次要计划,涉及外部激光源的使用,例如外部激光小型可插拔模块(External Laser Small Form Pluggables,简称ELSFP),以延长共封装光学设备的可靠性和使用寿命。COBO规范的主要目标是通过为系统制造商、集成商、组件制造商以及8通道和16通道板载光学设备的供应商提供通用规范,确保最终用户能够使用一致的技术平台。

共封装光学(CPO)设备的关键应用领域

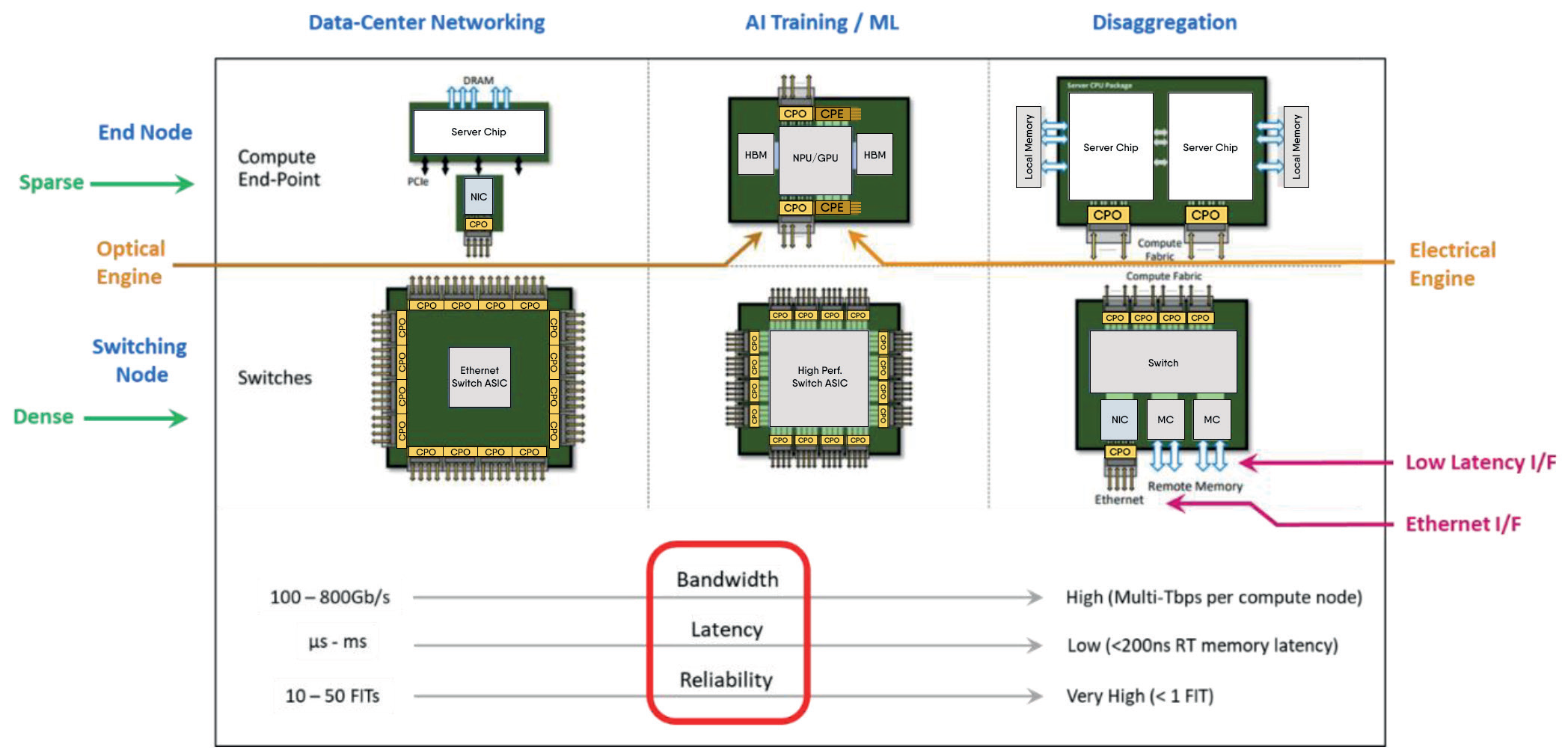

OIF确定了以下三个关键应用领域,这些领域将从共封装光学设备提供的低功耗和高带宽中受益匪浅:

• 数据中心以太网网络接口控制器(NICs)、连接服务器和存储设备的交换机

• 用于训练和机器学习的AI GPU接口

• Disaggregation

尽管每个应用都有其独特的需求,并且运行在不同的环境中,但每个用例都有相同的架构需求,包括两个具有高带宽需求的通信端点。图2展示了如何配置共封装光学设备以满足这些独特应用的需求。

图2: 共封装光学设备的潜在架构,可以满足不同应用的带宽、延迟和可靠性需求。来源:OIF论坛

共封装光学设备的构建模块:3.2Tb/s光模块

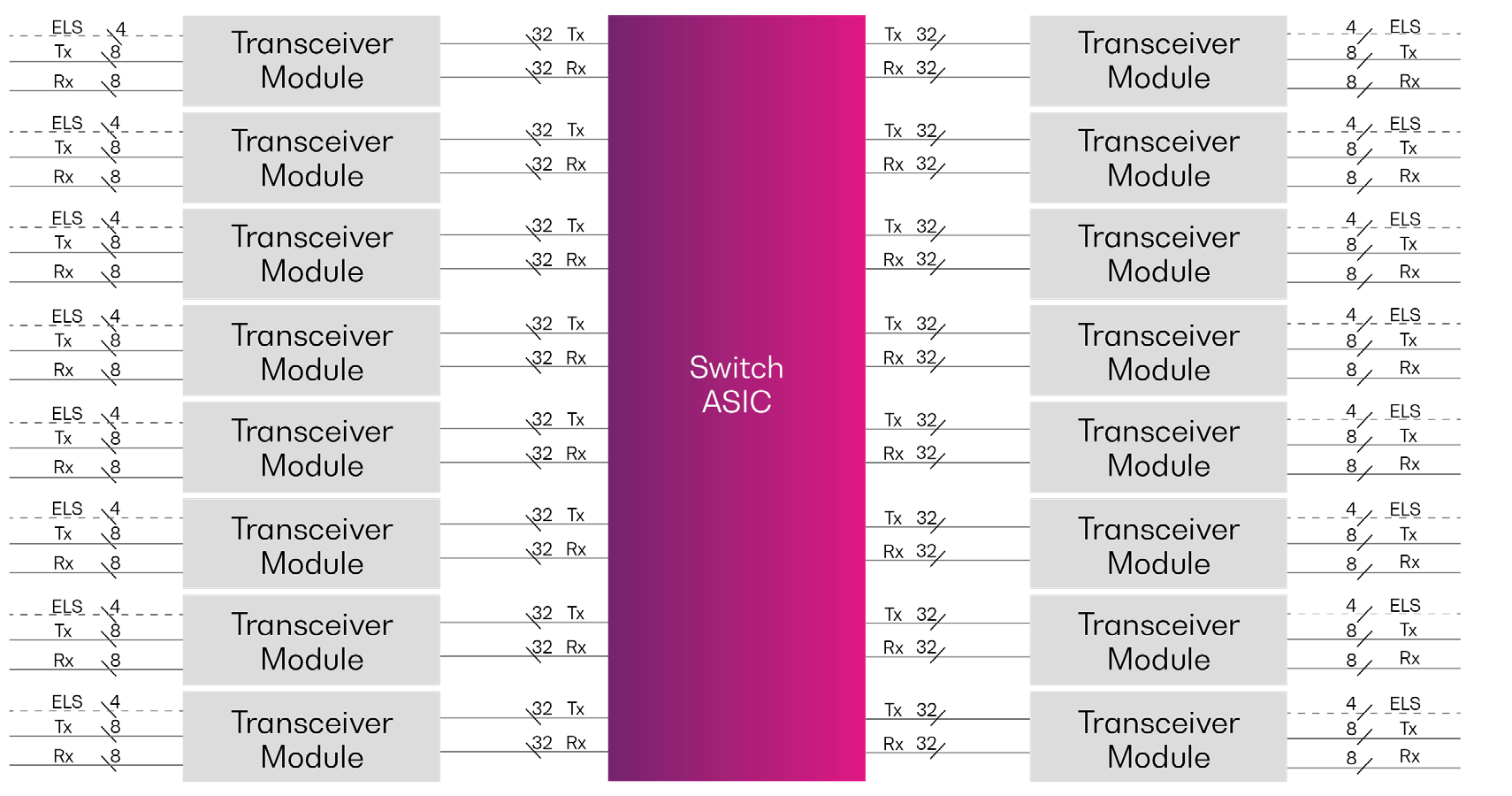

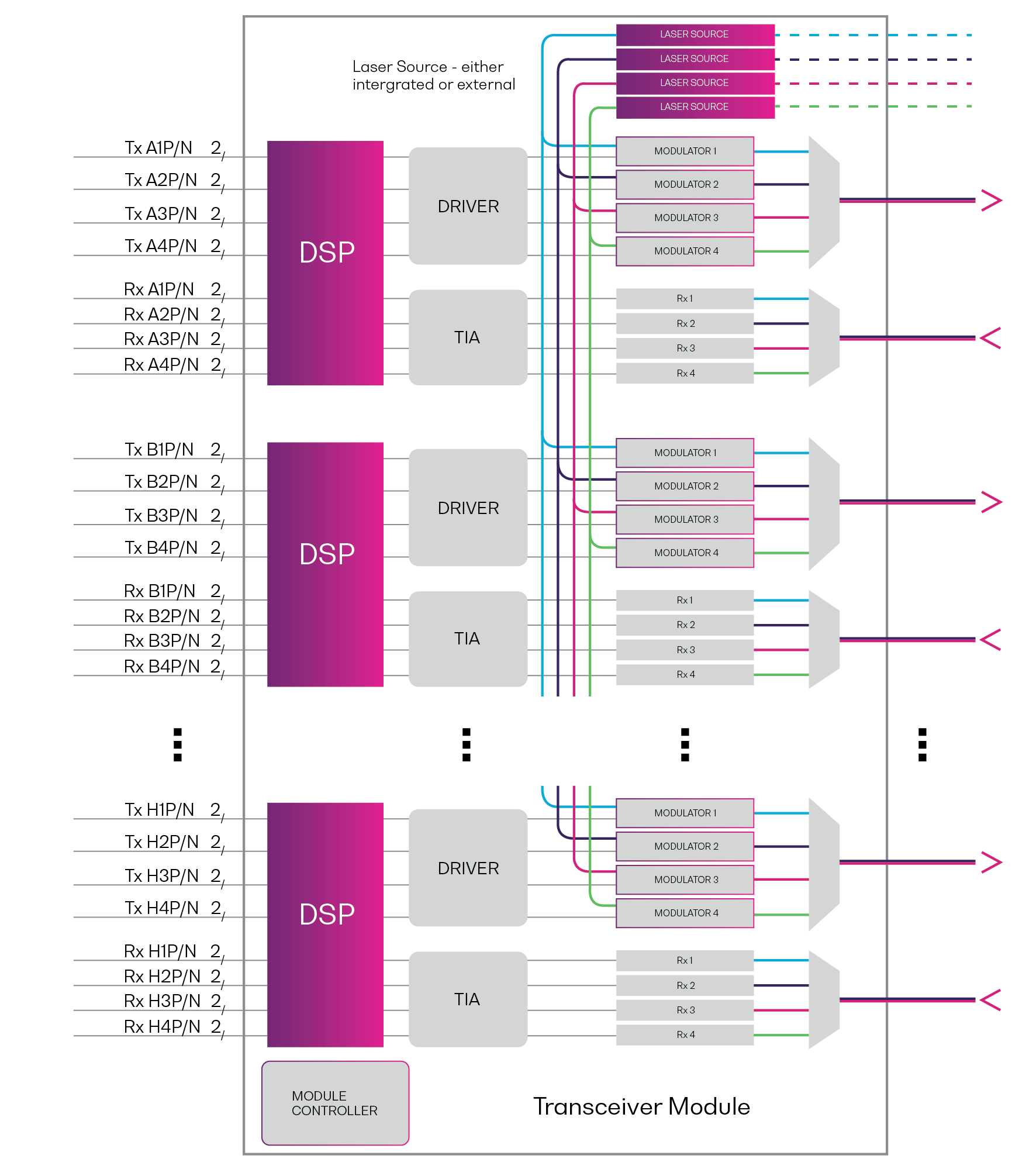

2021年,OIF启动了一个项目,旨在为开发3.2Tb/s模块(以及最终的6.4Tb/s模块)提供框架,这些模块将成为51.2Tb/s交换机的构建模块。最终,OIF和COBO提出的架构基于51.2Tb/s交换机,其中包括16个3.2Tb/s模块,这些模块被安排在ASIC附近,如图3所示。

图3: 400GBase-FR4 3.2Tb/s模块的系统框图

目前,许多参与3.2Tb/s共封装光学模块实施项目的OIF成员正在开发400GBASE-FR4和400GBASE-DR4选项,这些选项与200G接口兼容。虽然这些设备的所有要求都详细记录在产品需求文档(PRD)中,但该项目的一些关键指导原则包括以下内容:

• 模块应包括数字信号处理器(DSP)、调制驱动器、跨阻放大器(TIA)芯片以及基于硅光子学的光发射/接收组合,无论操作模式如何。

• 收发器的电气接口应基于32×106G电气通道,符合CEI-112G-XSR标准,电气接口速率在200BASE-FR4操作时应降至32×53G PAM4。

• 为了保持模块尺寸尽可能紧凑,不应有内置电源单元。由于光学和电气接口是这些模块的关键组成部分,让我们进一步探讨OIF框架为这些组件提供的指导。

光学接口

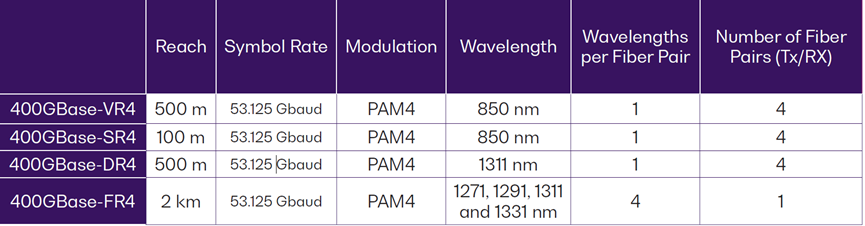

根据OIF框架,共封装光学模块应基于现有的光学接口标准,包括VR4、SR4、DR4和FR4。如表1所示,400GBase模块具有不同的传输距离、波长和通道数量。根据所选标准,需要不同的测试参数。

表1: 使用不同常见标准设计的光学接口规格概览

由于这些光学接口所使用的标准与当今可插拔模块所使用的标准相同,因此共封装模块与可插拔设备之间的互操作性得以保留。因此,数据中心可以使用带有可插拔模块的光纤分支电缆,以实现可插拔模块和共封装模块的最佳组合,从而满足其需求。

电气接口

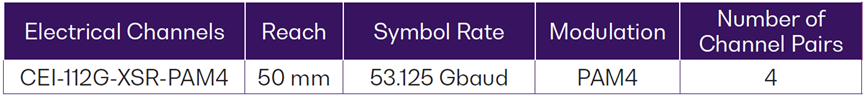

尽管共封装应用可能会使用多种电气接口标准,如XSR、LR、PCIe或AIB,但OIF框架主要关注使用XSR。表2中显示了一个使用XSR的模块示例。

表2: 使用XSR标准的模块电气接口规格

此外,OIF框架建议在共封装光学模块中可以使用以下四种电气接口选项:

• 重定时(Retimed):使用表2中详细描述的CEI-112G-XSR-PAM4实现,设计用于在约50毫米的第一级封装基板上实现ASIC和光引擎之间的低误码率通信。

• 线性放大(Linear Amplified):在引擎中消除CDR/DSP功能以降低功耗,ASIC中的发射和接收功能具有更多的放大和峰值调整,以便SerDes能够补偿整个链路。

• 半重定时(Half Retimed):引擎和ASIC通信的一半进行重定时,另一半采用线性放大方法。

• 直接驱动(Direct Drive):这是一种简化的接口,仅提供支持线性光通信通道所需的功能。

关于OIF框架和光模块PRD中提出的电气和光学接口规格的更多详细信息,请参阅相关文档。

共封装光模块激光器放置

随着社区致力于开发3.2Tb/s模块,关于激光器的放置位置——内部还是外部——存在争议。由于激光器是模块中最容易老化且产生大量热量的组件,因此在使用内部激光器时,可靠性和系统散热是需要考虑的问题。为解决可靠性问题,一个提议是在模块中包含一个备用激光器以实现冗余。然而,这种方法的缺点是会增加模块的尺寸,这对于许多应用来说是不理想的。

OIF社区成员也在通过之前提到的ELSFP模块项目研究激光器的外部放置。外部激光器的放置使组装更小,消除了使用内部激光器相关的热挑战,并且通常提高了模块的可靠性。然而,使用外部激光器的最大缺点是耦合激光进入模块的插入损耗会增加。为了补偿这一点,激光器的输出功率需要达到每个波长22dBm,这将增加能耗。

应对共封装光学设备的三大测试挑战

新技术的开发总会为光学工程师带来新的测试挑战。为了确保新设备的快速实施和部署,从资格认证到大批量生产的测试需求应该与设备开发同步进行。虽然本文的前半部分关注了共封装光学设备开发的一些关键要素,但接下来的重点将转向审视生产这种技术所面临的三大主要测试挑战。

挑战1:快速执行组装测试如前所述,共封装光学设备由多个单独的收发器模块组成——例如,一个51.2Tb/s的共封装设备包含16个3.2Tb/s的模块。每个收发器模块由来自一个或多个晶圆的芯片组装而成。为了减少在组装过程中后期出现问题的可能性,可以借鉴数十年高容量半导体制造的经验,将其应用于共封装光学设备所需的光测试中。让我们来审视一下这种测试方法所需的测试阶段:

• 晶圆测试

• 模块测试

• 共封装组装测试

晶圆测试

晶圆测试是第一个关键的测试步骤,因为这是发现故障成本最低的环节。一旦投入资源将晶圆切割并制成模块,制造商需要确保组成模块的组件符合规格。为了确保没有关键性能问题影响产量,需要在制造过程的早期进行高吞吐量的晶圆级测试。然而,对于硅光子学的测试存在诸多挑战。

尽管晶圆测试与半导体晶圆测试有一些相似之处,但光子测试与电子测试截然不同。例如,电学测试可以通过探针卡建立导电连接来完成,但对于光测试,需要精确对准以将光耦合进出光子组件。为了实现注入和捕获这些测试所需的光,需要通过机器人操作光学探针在晶圆周围移动。此外,为了在高容量下进行这些测试,需要快速主动对准。Quantifi Photonics的对数模拟功率计是专为晶圆测试设计的设备的一个例子,它允许非常快速的光纤对准。

图4:一种潜在模块配置的示例。来源:OIF论坛。

模块测试

模块是通过将通过晶圆测试的芯片封装在一起,并连接模块所需的其他元件(如激光器、放大器、调制器和信号处理所需的基本元件)组装而成的。模块测试是首次有机会测试一个单元的完整性能。这可以包括多种测试,例如检查调制光信号、激光器、热循环以及模块的校准,还可以包括在所需传输距离范围内对整个模块进行环回测试和误码率测试(BERT)。

在这一级别的测试中,可能会面临一些挑战。首先,模块可以使用多种不同的光和电标准,如本文第一部分所讨论的,这意味着需要了解并测试每种模块配置的不同性能标准。一开始,产量预测将决定测试站是针对单一类型的模块(例如850nm多模的SR4)进行定制,还是应该能够配置为处理多种类型(例如SR4和FR4,它们使用不同类型的光纤和波长)。

此外,在一个3.2Tb/s的模块中,有8根光纤,每根光纤有8个波长,这意味着有64个通道需要测试。如果没有支持并行测试的测试设备,就需要多个切换矩阵来在多光纤阵列的不同光纤之间切换,或者将不同波长切换到示波器中进行TDEQ测量。这种切换方法不仅耗时,而且可能会增加测试成本,因为它需要时间来切换测试。

相反,支持快速并行测试的高密度测试设备(例如我们的BERT)是一种更好的测试这些模块的方法。通过这种高密度、多通道的测试设备,用户可以灵活地以多种方式执行测试。例如,可以同时测试8根光纤,并对波长进行并行测试的解复用。

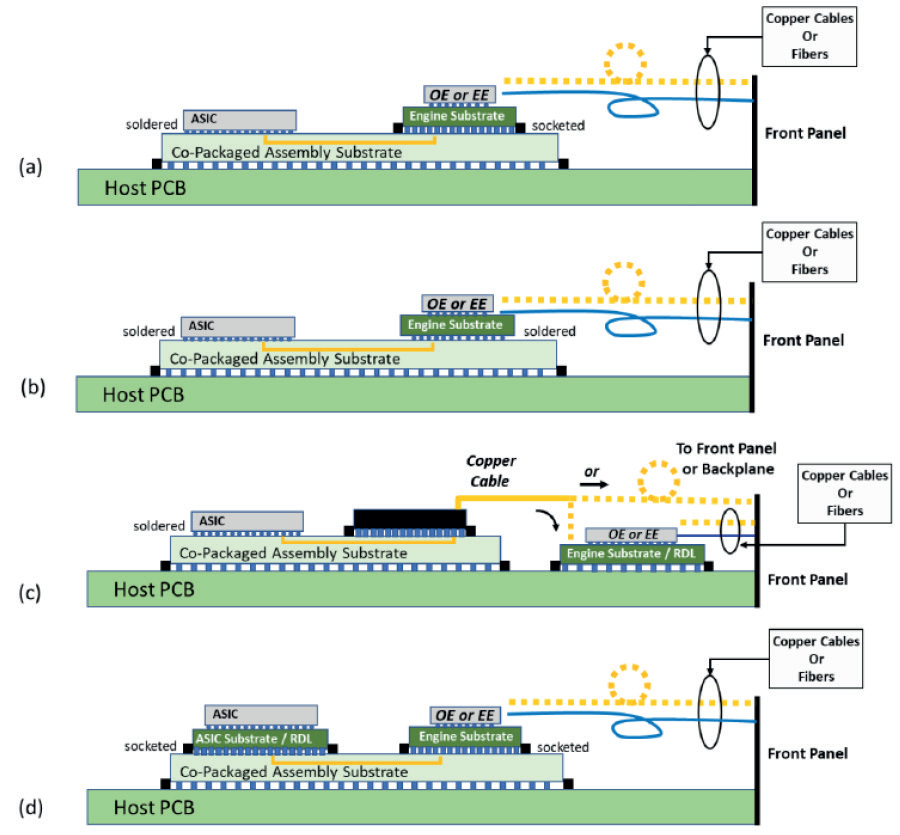

共封装组装测试

这一最终级别的测试涉及将经过充分测试的模块与ASIC和其他必要组件集成后的测试。一些可能的共封装组件的组装选项如图5所示。

图5: 共封装光学设备的四种不同组装选项。来源:OIF论坛

在这一点上,需要进行功能测试,以确保所有组件都被正确集成,没有引入制造缺陷,例如模块错位、光纤被夹住或端口损坏。然而,在组装测试中,测试挑战再次增加。例如,如果一个组装件包含8个模块,每个模块有8根光纤和每根光纤8个波长,那么现在总共有512个通道需要测试。因此,如果单通道模块测试需要一分钟来完成,那么使用单通道测试方法测试所有512个通道是不切实际的。

因此,在生产线和商业测试测量供应商努力跟上的情况下,并行测试是一个关键的成功因素。能够扩展到执行多达288通道并行测试的高密度功率计等测试设备是进行这些组件性能和光信号功率的快速测量所必需的。

挑战2:并行组装需要并行测试

传统上,光学设备在所有组件组装完成后才会进行测试。虽然这种方法可以加快设备的组装速度,但它可能导致需要增加测试覆盖率,并且会对产量产生不利影响。相反,最好在设备组装过程中进行测试,因为这种方法可以即时提供反馈,以确保组装成功。

让我们来看一个简单的例子,比较这两种测试方法。如果使用传统的“先组装后测试”方法来组装一个带有MPO-24光纤带的设备,那么在组装过程中进行测试可能只会对光纤带中的一个光纤进行测试,以确保组装方法有效。假设这种组装方法对其他光纤也有效,但实际上,为了优化其中一个光纤的性能,可能会牺牲其他23个通道的性能。然而,如果使用能够进行并行组装和测试的设备,就可以优化整个光纤带的组装。为此,需要能够提供多通道测试的测试仪器,例如激光器、功率计、衰减器和光开关。

挑战3:消除被占用的仪器

在进行并行测试时,确保测试仪器的最优利用是一个棘手的问题。在并行测试操作中,很容易出现被占用的仪器,或者仪器在测试站中被低效使用的情况。例如,当使用光谱分析仪(OSA)进行测试时,可能只需要80毫秒,而使用其他仪器进行PAM4 TDEQ测试可能需要数十秒。在这种情况下,仅需要80毫秒的仪器大部分时间可能会闲置。

为了最大化仪器利用率并降低测试系统的总成本,最好优化测试流程,将串行和并行测试结合起来使用。这种测试方法需要灵活的光开关来拆分并行端口,或者同时移动并行端口,以提供从并行通道中提取某些通道或将通道移动所需的灵活性。

克服当前的测试挑战并为未来做好准备

为了满足许多应用对带宽需求的快速增长,同时不显著增加能源消耗和网络应用的占地面积,共封装光学设备是一个有前景的解决方案。尽管许多组织正在合作开发这些模块所需的技术,但必须考虑并克服这些设备当前和未来的测试挑战。

在Quantifi Photonics,我们认识到提供高通道数、高密度测试设备的紧迫性,这将有助于推动共封装光学设备的广泛采用。我们已经推出了几款能够满足部分测试需求的产品,并制定了详细的路线图,以帮助解决这些测试的瓶颈问题。作为我们的愿景的一部分,我们致力于帮助光子学行业实现通常在电气半导体测试中常见的全自动化水平。我们设想的未来是,高吞吐量测试不仅成为可能,而且使用的测试仪器还将提供方便且紧凑的形式,帮助公司继续优化其测试设置并快速创新。